# Computation is Power時代のCircuit Simulation

学習駆動コース今岡ゼミ中田賢吾

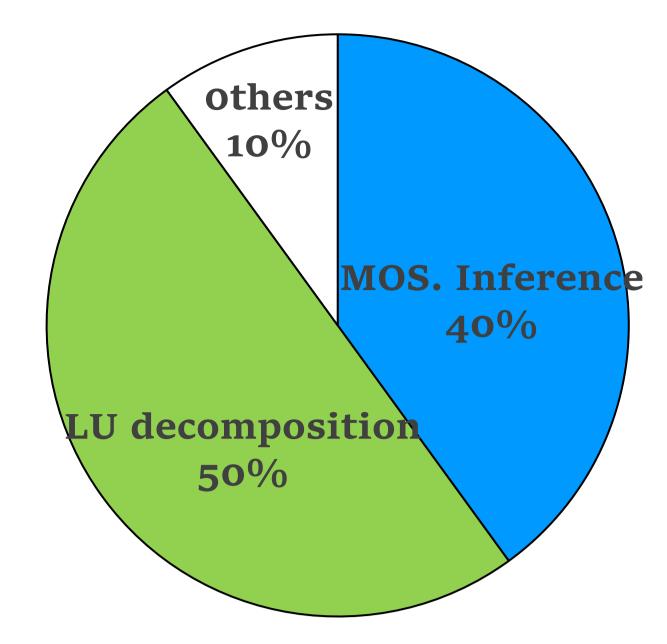

図1 シミュレーションに占める割合[1]

### 実測のデータ (離散値)を 数式にする必要がある モデル (デバイスモデル) MOSFET(W, L,...)

図2 デバイスモデルへの変換

## 解決手法(1)

Gate Voltage

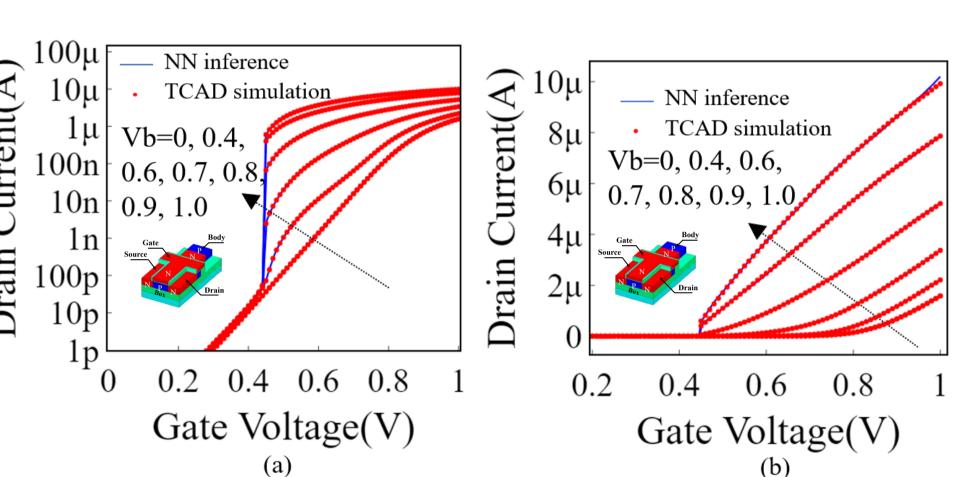

### GPUとの親和性が高い、 ニューラルネットワー ク(NN)モデリング

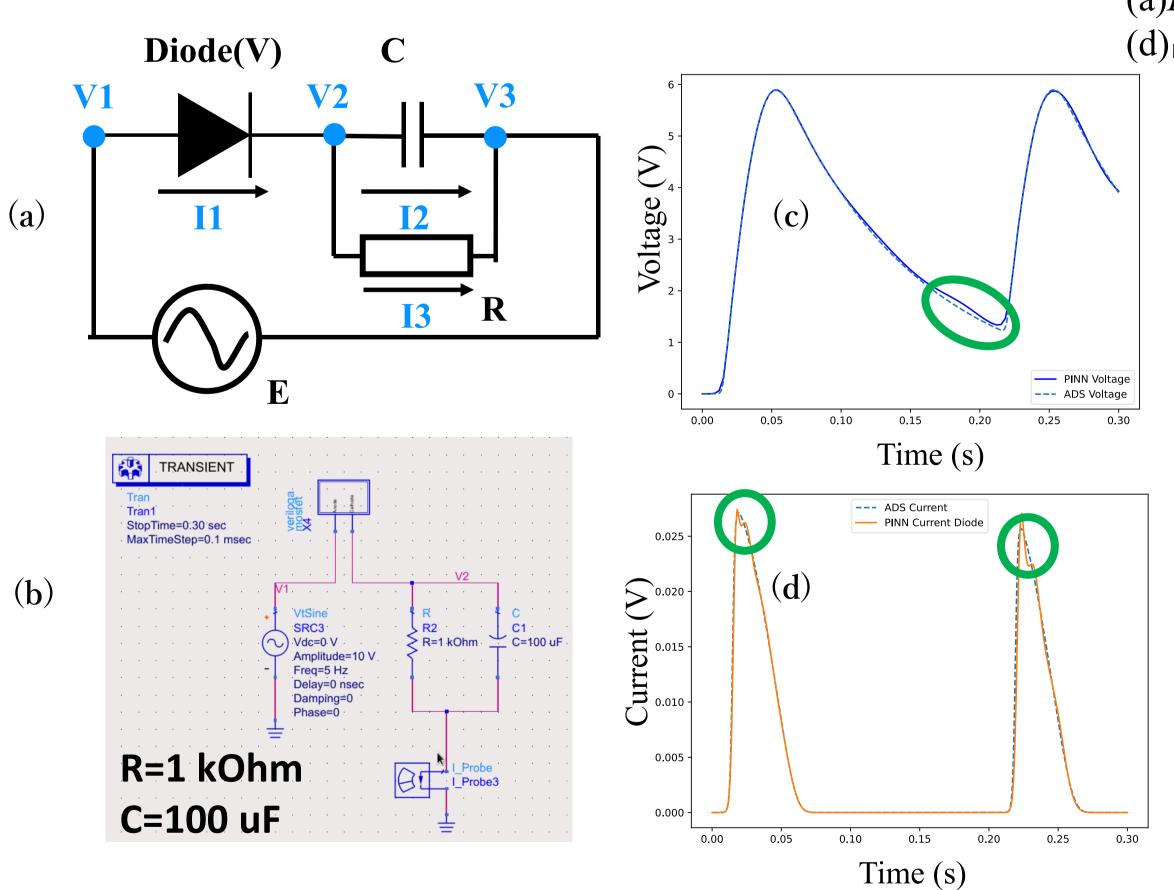

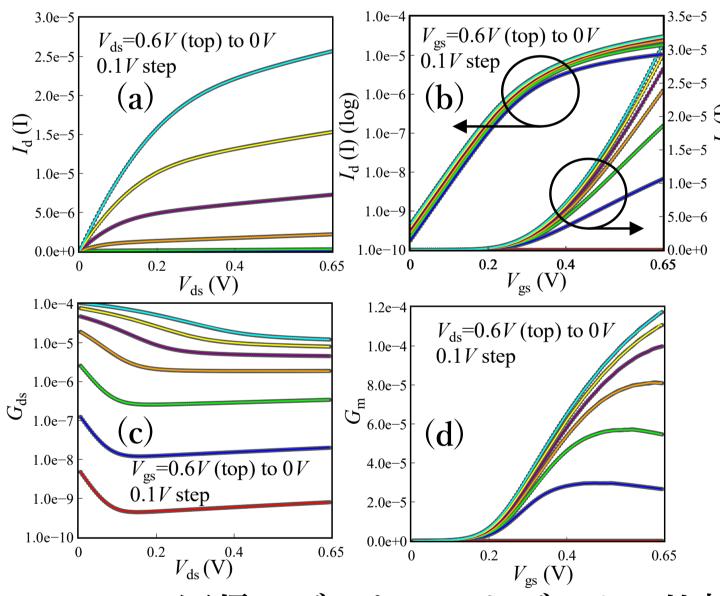

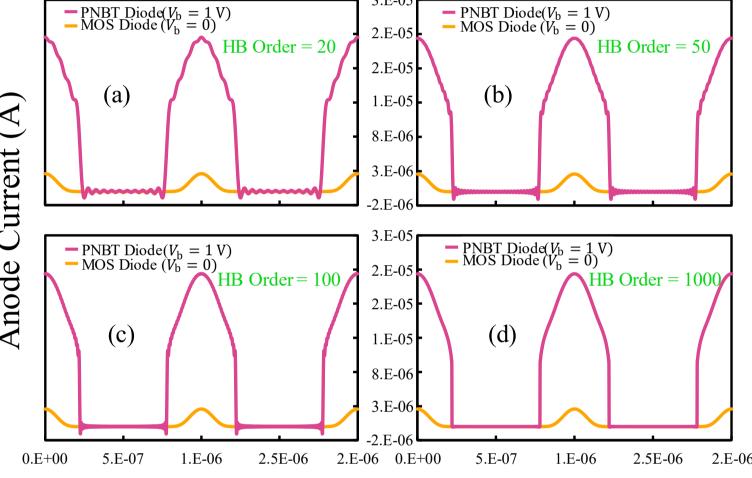

GPUやCPUでの高い並列処理性能、新規デバイスへ の適用や線形領域での高精度化が実現できるNNモデ ルの活用を行った。図3に物理式ベースのモデルが現 状存在しないPN-Body Tied (PNBT) SOI-FETのモデリ ングの結果を示す。線形表示、片対数表示の両方でう まくモデリングが出来ている。また、商用回路シミュ レータであるADSにNNモデルを組込みハーモニック バランス(HB)シミュレーションで半波整流シミュ レータを行った結果を図4に示す。NNモデルを使って も回路シミュレーションが可能であることが分かる。 MOSFETのモデリングの結果と先行研究の比較結果を 図4と表1に示す。MOSFETにおいても高精度にモデリ ングが出来ていることが分かる。

図7 PINNを用いたSOLVERでの半波整流の過渡応答sim結果と回路図 (a) 半波整流の回路図 (b) ADSでの構成図 (c) 電圧-時間グラフ (d)電流-時間グラフ

本研究は、JST-CREST (JPMJCR20Q1) の支援を受けたものである。 会社の協力を受けています。

ズ株式会社およびシーメンス EDA ジャパン株式会社およびキーサイト・テクノ ロジ株式会社の協力で行われたものである。

### 概要

### 既存の回路シミュレータは遅い!! 原因はデバイスモデル、SOLVERにある。

①MOSFETの演算に要する時間は40%と非常に大きい(図1)。このMOSFETのモ デルを作成するには離散値を連続値に変換してモデル化する必要がある(図2)。 このモデルの演算を高速化することが重要である。大規模集積回路において、

### デバイスモデルの種類 << 使用する素子数となる

そのため、1つのモデルで膨大な数の条件を計算する必要があるが、各条件に依 存関係が生じないため並列処理が可能である。そのためGPUでデバイスモデルの 計算を行うことで高速化が実現できる。しかし、現行のデバイスモデルは、物理 式ベースのモデルであり、GPUでの計算にあまり向いていないこと、近年の微細 化、新規デバイスへのモデリングへの対応に非常に時間が掛かることや線形領域 での精度が悪いなど多くの問題がある。

②過渡応答シミュレーションはSOLVERに問題があり、長時間のシミュレーショ ンを行うのが難しい。過渡応答シミュレーションは、微分方程式を解く際に積分 をするために前の時間の解が分からないと解けない。従って必然的に逐次処理と なる。2004年頃からCPUの動作周波数は大きくは改善されていないため<mark>逐次処理</mark> を行う現行のSOLVERには大きな問題がある。

図3 PNBT SOI FETでのモデリングの結果 (a)片対数表示、(b)線形表示

図4 HBシミュレーションでのMOS Diodeと PNBT Diodeの結果 (a)20次、(b)50次、 (c)100次、(d)1000次

#### 表1 先行研究とのバラツキ $(3\sigma)$ の比較

|                      | Our (Linear) | Our (NN) | [2]        | [3]        |

|----------------------|--------------|----------|------------|------------|

| BSIM                 | ×            | ×        | $\bigcirc$ | $\bigcirc$ |

| Gradient information | ×            | ×        | $\bigcirc$ | ×          |

| Id $(3\sigma)$       | 0.02%        | 0.14%    | 1.30%      | 1.09%      |

| $Gm(3\sigma)$        | 0.12%        | 0.36%    | 4.10%      | 2.97%      |

| Gds $(3\sigma)$      | 0.23%        | 2.07%    | 2.90%      | 6.61%      |

| NN model             | ×            | 64-32    | 8-8-8      | 28         |

| Plolynominal degree  | 34           | X        | _          | _          |

図6 MOSFETでの回帰モデルとテストデータの比較結果  $(a)I_{d}$ - $V_{gs}$ 特性  $(b)I_{d}$ - $V_{ds}$ 特性 (c)トランスコンダクタンス (d)出力コンダクタンス

### 解决手法②

### PINNを活用した並列処理可能な 微分形SOLVERの提案

Physics-Informed Neural Networks (PINN)を使って微分方程式を微分形で解く ことで、並列処理可能であるかの実験を行った結果を図6に示す。積分形では 前の時間が正しくないと正しい答えが求まらないが、PINNを用いた本手法で は、影響を受けずに並列処理が可能であることが分かる。また、ニューラル ネットワークを活用しているためGPUへの移植性も非常に高い。

### 今後の展望

### CPUやGPUなどの大規模集積回路の 過渡応答シミュレーション検証

CPUやGPUなどのASIC設計において長時間の過渡応答シミュレーションを 行えるようになれば、GPUの台数を増やすだけで、飛躍的にシミュレーショ ンできる領域が格段に向上する。また、アナログ回路、SRAMやCMOSイ メージセンサなど様々な領域で活用が期待できるため今後更なる検討を行う 必要がある。

#### 参考文献

[1] 小川 公裕,アナログ回路設計現場におけるSpice回路シミュレータの理論と使い方, 情報機構 本研究は、高エネルギー加速器研究機構 (KEK)およびラピスセミコンダクタ株式 [2] M.-Y. Kao, H. Kam, and C. Hu, "Deep-Learning-Assisted Physics-Driven MOSFET Current-Voltage Modeling," IEEE Electron Device Lett.

本研究は、東京大学VDEC 活動を通して、日本ケイデンス・デザイン・システム [3] K. Sheelvardhan, S. Guglani, M. Ehteshamuddin, S. Roy, and A. Dasgupta, "Machine Learning Augmented Compact Modeling for Simultaneous Improvement in Computational Speed and Accuracy," IEEE Trans. **Electron Devices**